**Preliminary**

**SM9714**

### **FEATURES**

- VCM driver for auto-focus

- 10 bit resolution current sinking of 120mA for VCM

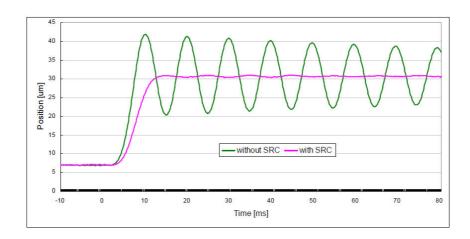

- VCM slew rate control (SRC) Linear slope control, Dual level control

- Supply voltage range (VDD): 2.3V to 3.6V

- Fast mode I2C interface (1.8V interface available)

- Power on reset (POR)

- Package: 0.82mm(W) \* 1.32mm(H)\*0.3mm(T)

- 6pins WLCSP

## **APPLICATIONS**

- Cell Phone Auto Focus

- Web and PC cameras

- Security cameras

- Image stabilization

#### DESCRIPTION

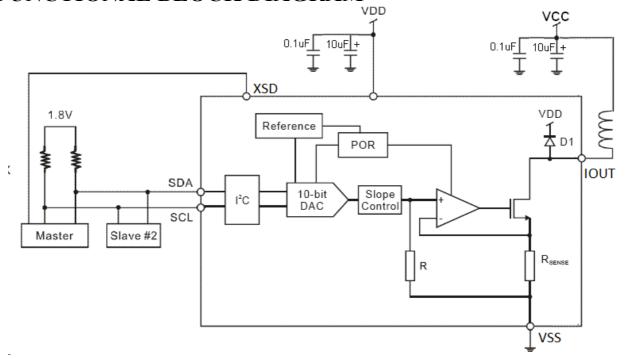

The SM9714 is single 10-bit DAC with 120mA output current sink capability. Designed for linear control of voice coil motors, the SM9714 is capable of operating voltage to 3.6V. The DAC is controlled via a I2C serialinterface that operates DAC by clock rates up to 400kHz. The SM9714 incorporates with a power-on reset circuit, power-down function, and exactly matched sense resistor. Power-on reset circuit ensure when supply power up, DAC output is to 0V until valid write-bit value takes place. It has a power down features that reduces the current consumption of the device to 1uA maximum. The SM9714 is designed for auto focus and optical zoom camera phones, digital still cameras, and camcorders applications. The I2C address for the SM9714 is 0x18.

### FUNCTIONAL BLOCK DIAGRAM

SM9714 Preliminary -1 - www.semihigh.com.cn Dec 2012

**Preliminary**

SM9714

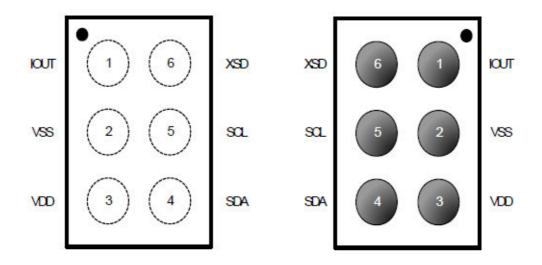

### PIN CONFIGURATION AND PIN DESCRIPTION

### WCSP-6

Top View Bottom View

IC size: 0.81(W) X 1.31(L) X 0.30(T) (mm) Minimum pin pitch = 0.4mm (6pins WLCSP)

### PIN DESCRIPTION

| No. | Pin name | I/O | Description                        |

|-----|----------|-----|------------------------------------|

| 1   | IOUT     | 0   | Output current sink                |

| 2   | VSS      | -   | Ground                             |

| 3   | VDD      | -   | Power supply                       |

| 4   | SDA      | I/O | I2C interface input (DATA)         |

| 5   | SCL      | I   | I2C interface input/output (CLOCK) |

| 6   | XSD(1)   | I   | Shutdown mode (active low)         |

(1) XSD : Shutdown mode (active low)

1: Normal operation

**Preliminary**

SM9714

#### ABSOLUTE MAXIMUM RATINGS

(Unless otherwise specified, Ta=25 $^{\circ}$ C)

| Symbol                | Parameter             | Min  | Max                          | Unit                    |

|-----------------------|-----------------------|------|------------------------------|-------------------------|

| VBB <sub>DDBB</sub>   | VDD to GND            | -0.3 | 4.5                          | V                       |

| Vin                   | Control input voltage | -0.3 | VDD+ 0.3                     | V                       |

| Vhbm                  | Human body model      |      | 2                            | KV                      |

| Vmm                   | Machine model         |      | 200                          | V                       |

| IBB <sub>SINKBB</sub> | ISINK to GND          |      | -0.3 ~ V <sub>DD</sub> .+0.3 | V                       |

| Topr                  | Operating temperature | -45  | -40 ~ +85                    | $^{\circ}\!\mathbb{C}$  |

| Tstg                  | Storage temperature   |      | <b>-</b> 65 ∼ +150           | $^{\circ}\! \mathbb{C}$ |

| Tjmax                 | Junction temperature  |      | 150                          | $^{\circ}\!\mathbb{C}$  |

Note> Continuous Power Dissipation (Ta=25 $^{\circ}$ C) 0.82mm X 1.32mm WLCSP, 100 $^{\circ}$ C/W

Use of the IC in excess of absolute maximum ratings such as the applied voltage or operating temperature range(Topr) may result in IC damage. Assumptions should not be made regarding the state of the IC (short mode or open mode) when such damage is suffered. The implementation of a physical safety measure such as a fuse should be considered when use of the IC in a special mode when the absolute maximum ratings may be exceeded is anticipated.

### RECOMMENDED OPERATING CONDITION

| Symbol | Parameter                 | Min. | Тур. | Max. | unit |

|--------|---------------------------|------|------|------|------|

| VDD    | Power supply voltage      | 2.3  | 2.8  | 3.6  | V    |

| Vin    | Control input voltage     | 1.8  | 2.8  | VDD  | V    |

| SCL    | I2C bus transmission rate |      |      | 400  | K HZ |

#### Note:

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Preliminary**

SM9714

## **ELECTRICAL CHARACTERISTICS**

(VDD=2.3 to 3.6V, Vin=1.8V to VDD, Ta= -40 to 85  $^{\circ}$  , unless otherwise specified. Typical values are at 25  $^{\circ}$  )

| n ,                         | G 1.1           | C PV                     |      | Rating |      | <b>T</b> T •4 |

|-----------------------------|-----------------|--------------------------|------|--------|------|---------------|

| Parameter                   | Symbol          | Conditions               | Min. | Typ.   | Max. | Unit          |

| DC Performance              |                 |                          |      |        |      |               |

| Supply Voltage              | VDD             |                          | 2.3  |        | 3.6  | V             |

|                             | Isd             | Shutdown mode            | -1   |        | +1   | uA            |

| VDD Current                 | IPD             | Power down mode          | -1   | -      | +1   | uA            |

|                             | IQ              | Quiescent mode           | 0.24 | -      | 0.35 | mA            |

|                             | Log             | ic input / output (XSD)  |      |        |      |               |

| Input current               |                 |                          | -1   | -      | +1   | uA            |

| Low Level Input Voltage     | VIL             | -                        |      |        | 0.54 | V             |

| High Level Input Voltage    | V <sub>IH</sub> | -                        | 1.26 |        |      | V             |

|                             | Logic           | input / output (SCL,SDA) |      |        |      |               |

| Input current               |                 | -                        | -1   |        | +1   | uA            |

| Low Level Input Voltage     | VIL             | -                        |      |        | 0.54 | V             |

| High Level Input Voltage    | Vih             | -                        | 1.26 |        |      | V             |

| Glitch rejection            |                 |                          |      | 50     |      | nS            |

|                             |                 | VCM driver               |      |        |      |               |

| Current resolution          |                 | 117.3uA/LSB              |      | 10     |      | bits          |

| INL                         | INL             |                          | -4   | -      | +4   | LSB           |

| DNL                         | DNL             |                          | -1   | -      | +1   | LSB           |

| Zero code error             | ZCE             | Zero data loaded to DAC  | -1   | -      | +1   | mA            |

| IOUT compliance voltage (1) |                 | Output current = 100mA   | 150  | -      | -    | mV            |

| Maximum output current      | Imax            |                          |      | 120    |      | mA            |

| Power on time (2)           | TPON            |                          |      | 0.5    |      | ms            |

**Preliminary**

SM9714

- (1) The output compliance voltage is guaranteed by design and characterization, not mass production test.

- (2) SM9714 requires waiting time of 0.5ms after power on. During this waiting time, the offset calibration of internal amplifier is operating for minimization of output offset current .

- (3) Maximum output current can be set 60mA to 140mA.

**Preliminary**

**SM9714**

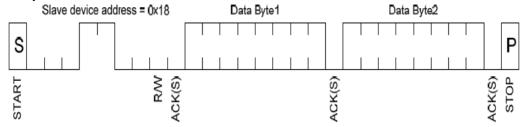

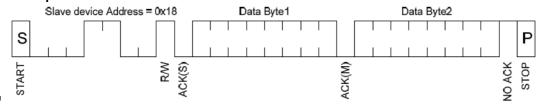

## REGISTER 12C FORMAT

#### **■Write operation**

#### ■Read operation

#### **Register Format**

|    |          | Byte1 |    |    | Byte1 Byte2 |    |    |    |    |    |    |    |    |    |    |

|----|----------|-------|----|----|-------------|----|----|----|----|----|----|----|----|----|----|

| PD | FL<br>AG | D9    | D8 | D7 | D6          | D5 | D4 | D3 | D2 | D1 | D0 | S3 | S2 | S1 | S0 |

PD: Power down mode

1: Power down mode (active high)

0: Normal operation mode

FLAG: FLAG must keep "L" at writing operation.

D[9:0]: Data input

Output current = (D[9:0]/1023) X 120mA

Max current =  $120\text{mA} + \frac{1}{5}\%$

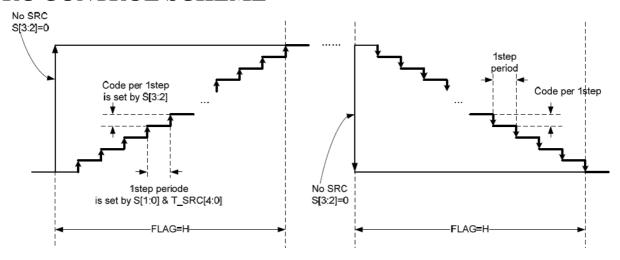

S[3:2]: Codes per step

| S[3:2] | Codes per step              |

|--------|-----------------------------|

| 0      | 0 (no SRC) - direct driving |

| 1      | 1                           |

| 2      | 2                           |

| 3      | 4                           |

#### S[1:0]: Step period

| SRCT[1:0] | Period [us] |

|-----------|-------------|

| 0         | 81          |

| 1         | 162         |

| 2         | 324         |

| 3         | 648         |

**Preliminary**

SM9714

## **SRC CONTROL SCHEME**

### **SRC TEST RESULTS**

**Preliminary**

**SM9714**

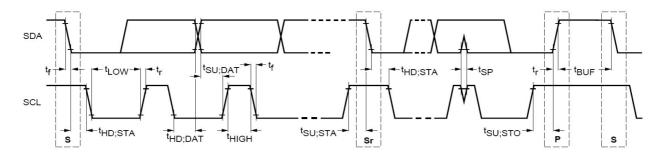

### **I2C PROTOCOL**

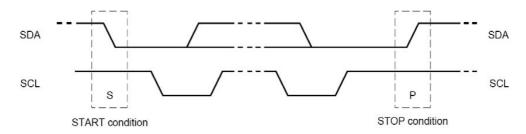

#### Start and Stop condition

Within the procedure of the I2C-bus, unique situations arise which are defined as START (S) and STOP (P) conditions. A HIGH to LOW transition on the SDA line while SCL is HIGH is one such unique case. This situation indicates a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition.

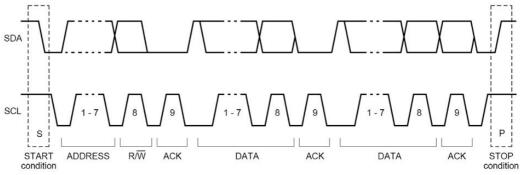

#### ■ Complete I2C Data Transfer

Data transfers follow the format. After the START condition (S), a slave address is sent. A data transfer is always terminated by a STOP condition (P) generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated

**Preliminary**

SM9714

## **I2C TIMING**

| Parameter                                        | Symbol                 | Min.                                | Max.     | Unit |

|--------------------------------------------------|------------------------|-------------------------------------|----------|------|

| SCL clock frequency                              | <b>f</b> SCL           | 0                                   | 400      | kHz  |

| Hold time (repeated) START condition.            | tHD;STA                | 0.6                                 | <u>u</u> | us   |

| Low period of the SCL clock                      | tLOW                   | 1.3                                 | <u> </u> | us   |

| High period of the SCL clock                     | <b>t</b> HIGH          | 0.6                                 | ā        | us   |

| Set-up time for a repeated START condition       | tsu;sta                | 0.6                                 | Ē        | us   |

| Data hold time                                   | tHD;DAT <sup>(1)</sup> |                                     | 0.9      | us   |

| Data set-up time                                 | tsu;DAT                | 100                                 | -        | ns   |

| Rise time of both SDA and SCL signals            | tr                     | 20+0.1C <sub>b</sub> <sup>(2)</sup> | 300      | ns   |

| Fall time of both SDA and SCL signals            | tr                     | 20+0.1C <sub>b</sub> <sup>(2)</sup> | 300      | ns   |

| Set-up time for STOP condition                   | <b>t</b> su;sto        | 0.6                                 |          | us   |

| Bus free time between a STOP and START condition | <b>t</b> BUF           | 1.3                                 | ē.       | us   |

| Capacitive load for each bus line                | Сь                     | æ                                   | 400      | pF   |

| Pulse width of spike suppress                    | tsp                    | 0                                   | 50       | ns   |

(1) A master device must provide a hold time of at least 100ns for the SDA signal to bridge the undefined region of the falling edge of SCL. The maximum tHD;DAT has only to be met if the device does not stretch the LOW period (tLOW) of the SCL signal.

(2) Cb is the total capacitance of one bus line in pF, tr and tf are measured between 0.3VDD to 0.7VDD.

SM9714 Preliminary - 9 - www.semihigh.com.cn Dec 2012

**Preliminary**

SM9714

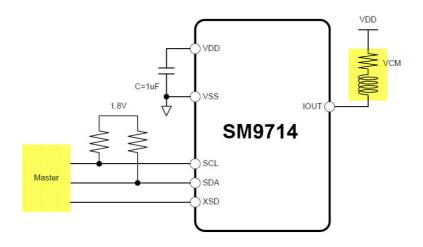

## TYPICAL APPLICATION CIRCUIT

**Preliminary**

SM9714

## **ORDER INFORMATION**

| Valid Part Number | Package Type | Top Code |

|-------------------|--------------|----------|

| SM9714            | 6 Pins, WCSP | 9714     |

**Preliminary**

SM9714

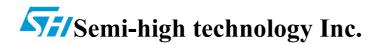

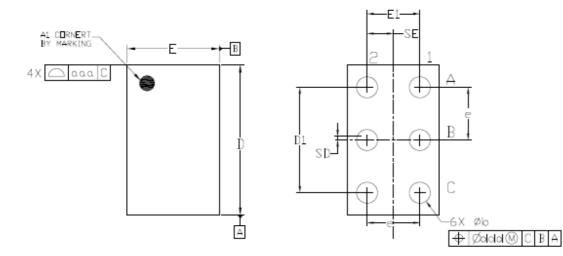

# PACKAGE DIMENSION (6 WLCSP 0.82 X 1.32 X 0.30)

\* Unit : mm *WCSP-6*

| Dimensional Ref. |           |         |        |  |  |  |

|------------------|-----------|---------|--------|--|--|--|

| REF.             | Min.      | Nom.    | Max.   |  |  |  |

| Α                | 0.260     | 0.300   | 0.340  |  |  |  |

| Α1               | 0.065     | 0.080   | 0.095  |  |  |  |

| A2               | 0.195     | 0.220   | 0.245  |  |  |  |

| D                | 1.270     |         | 1.350  |  |  |  |

| Е                | 0.770     |         | 0.850  |  |  |  |

| D1               | 0.750     | 0.800   | 0.850  |  |  |  |

| E1               | 0.350     | 0.400   | 0.450  |  |  |  |

| Ь                | 0.150     | 0.200   | 0.250  |  |  |  |

| e                | -0        | .400 BS | C      |  |  |  |

| SD               | 0         | .000 BS | C      |  |  |  |

| SE               | 0         | .200 BS | C      |  |  |  |

| To               | ol. of Fo | rm&Pos  | sition |  |  |  |

| aaa              | 0.10      |         |        |  |  |  |

| ььь              | 0.10      |         |        |  |  |  |

| CCC              | 0.05      |         |        |  |  |  |

| ddd              |           | 0.05    |        |  |  |  |